2022年3月24日、第5回AIエッジコンテスト「RISC-Vを使用した自動車走行画像認識」コンペティションの表彰式が開催されました。当日は、アイデア賞に選ばれた入賞者が表彰され、各入賞者による解法プレゼンテーションが行われました。プレゼンテーション終了後には質疑応答も実施。革新的なAIエッジ技術の実現に向けて、大きな一歩となる素晴らしい表彰式でした。

▼動画はコチラ▼

コンペティション概要

コンペティション事務局の大渕氏による進行のもと、まずはSIGNATE西氏より、コンペティション概要の説明が行われました。

株式会社SIGNATE データサイエンティスト 西 惇宏 氏

「それでは、私から本コンペティションの概要についてご説明させていただきます。このAIエッジコンテストは過去4回にわたって開催しており、AIエッジ技術へのチャレンジに加えて、優れた技術や人材、アイデアの発掘を目指すコンペティションとなっております。車両の走行画像に基づいた何かしらの課題を解いていくことをベースに、物体検出やセグメンテーションを行う内容になっています。今回は、車両の走行画像を用いて物体追跡をしていただきました。今回の課題について具体的に言うと、車両の前方に映っている人や乗用車をうまく追跡できるかが求められました。また、物体追跡をするにあたって、RISC-Vを実装し、使用することが条件となっていました。モデル作成から、ハードウェア実装まで行うかなりヘビーな課題だったため、多角的に評価できるよう、処理速度賞とアイデア賞、フォーラムで問題の解決に大きく寄与した方に贈られるフォーラム活動賞、そしてコンペティションに関するブログ記事を執筆していただいた方に贈られる記事執筆賞の4部門を設けました。今回のコンペティションを開催するにあたって、多くの団体様に協賛・後援いただき、またアドバイザリーとして多くの方々にご意見をいただきました。この場を借りて感謝申し上げます。」 続いて、大渕氏よりコンペティションの結果について説明が行われました。

AIエッジコンテスト運営事務局 大渕 栄作 氏

「それでは、今回のコンペティション結果について説明させていただきます。参加人数は243名、実際の投稿件数は113件、最終的な提出物提出は7チーム(9名)でした。審査結果としては、いずれのチームも認識精度の基準であるMOTA>0.6の基準が達成できなかったため、処理速度賞は該当者なしという結果となりました。また最後まで実装、動作させることができた3チームについては内容の審査の元、アイデア賞入賞とさせていただきました。この3チームの審査のポイントとしては、独自性やレポートの内容・質を考慮し評価しました。さらに、今後のコンテストにつながるか、RISC-V、FPGAに興味がある方に有益になるかといった点でも評価しております。三者三様、それぞれ特徴のある実装でしたので、後ほどのプレゼンテーションではそのあたりを注目していただければと思います。また、フォーラム活動賞は該当者はおらず、記事執筆賞は、今後のコンペティションに有益な情報を寄せていただいたlp6mさん、ミソジさんに贈られました。」

主催者あいさつ

その後、コンテスト主催者である経済産業省の荻野氏と、国立研究開発法人 新エネルギー・産業技術総合開発機構(NEDO)の石丸氏により、挨拶が行われました。

経済産業省 商務情報政策局 デバイス・半導体戦略室 室長 荻野 洋平 氏

「本日、このような会が開かれたことに対して皆様のご尽力に感謝申し上げます。今回のコンペティションは敷居が高い部分もあったと思いますが、最後まで走りきって下さった参加者の方々には深く御礼申し上げます。経済産業省としましても、半導体が我々の生活にとっていかに深く結びついているかを示していくことが大切だと考えております。その意味で、今回のコンペティションは大きな役割を持っていると思いますので、引き続き、お力添えいただけますと嬉しいです。」

国立研究開発法人 新エネルギー・産業技術総合開発機構(NEDO) IoT推進部 統括主幹 石丸 昌平 氏

「表彰式にご参加いただき、誠にありがとうございます。本コンペティションにおいてご指導いただいた方々、またご支援いただいた方々に深く御礼申し上げます。今後、IoT社会が本格的に到来しますと、扱うべき情報量がこれまでとは比べものにならないほど増大することが考えられます。そのときのためにも、AIエッジ技術を駆使し、情報処理の分散化を実現することが必要不可欠です。そうした背景のもと、AIエッジ技術のアイデアを生み出す人材を増やしていくために、今回のコンペティションを開催させていただきました。改めて、参加していただいた皆様に感謝申し上げます。」 また、AIエッジコンテスト ステアリング委員会委員長として、東京大学 加藤教授からも挨拶がありました。

東京大学大学院 情報理工学系研究科 情報科学科 准教授 株式会社ティアフォー 創業者兼最高技術責任者(CTO) 加藤 真平 氏

「AIエッジコンテストは、回を重ねるごとに徐々にハードルを上げているのですが、それは単に難しいことをやろうということではありません。今後社会実装をする上ではAIをアジャイルに開発するための技術が必要となってくるため、時代の先を読んで課題設定をしているのです。今回の課題もかなりハードルが高かったかもしれませんが、だからこそ10年後に振り返ったとき、『このコンペティションって先進的だったよね』と言ってもらえる内容になっていると思います。この取り組みが、日本や周辺各国の技術開発にとっていいヒントになり、アジャイルな視点を持って開発に取り組める人材やチームが増えることを願っています。」

入賞者の発表

表彰式はメインコンテンツである入賞者の表彰と、解法プレゼンテーションへ。まずはアイデア賞に入賞されたninfuengさんによる解法プレゼンテーションと質疑応答が行われました。

アイデア賞

ninfueng 氏

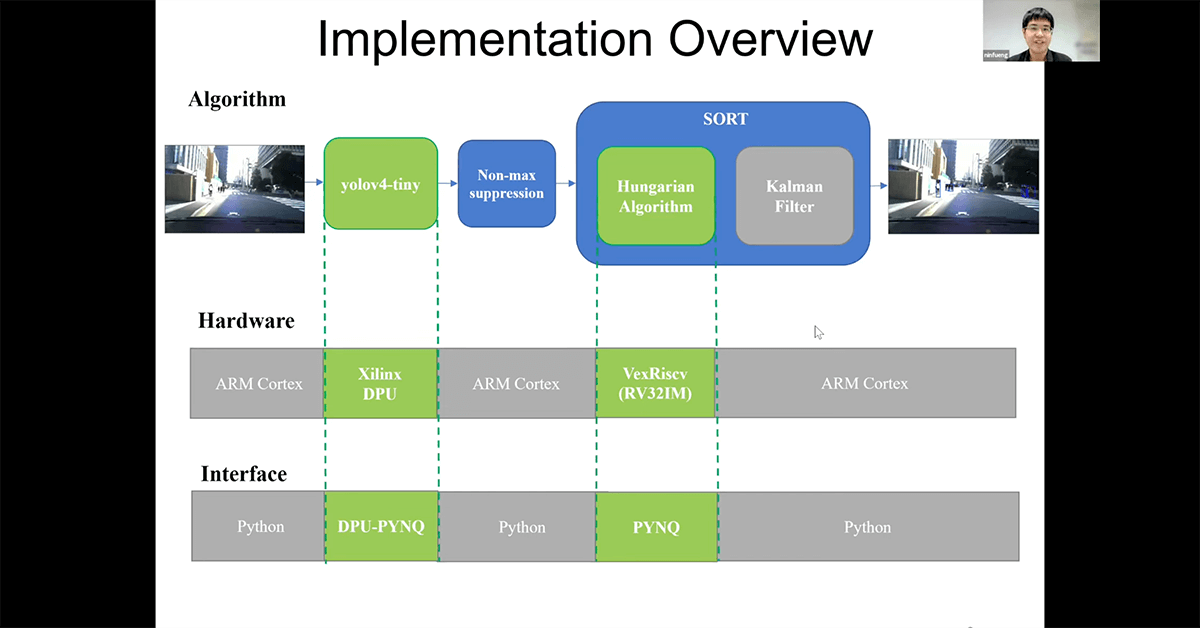

「今回のオブジェクトトラッキングの課題に対して、オブジェクト認識+トラッキングの処理の2つの処理タスクに分けて、それぞれYolo v4-tiny 及び、SORTのアルゴリズムを選択しました。オブジェクト認識処理のYolo v4-tinyについてはXilinxのDPUコア上にDPU-PYNQをインターフェイスとする実装、SORT内のHungrian algorithmはRISC-VコアであるVexRiscv上に実装し、その他のSORTアルゴリズム処理はARM Cortex CPU上で実行しています。Yolo v4-tinyによる物体認識では、認識結果であるアンカー矩形ボックスのサイズを小さくすることでスコアがよくなったことから、元結果に対して小さくなるよう細工を行いました。また、SORTによるトラッキングでは、入力行列サイズが小さくて済む+整数演算で構成されている背景からHungarian algorithmをRISC-V上に実装しています。RISC-Vコアは香港テスト向けに公開されたReferenceコアを用い、IMEM, DMEMのサイズを増やし実装しています。実装の結果、5.85fpsの実行速度及び、MOTA=0.2579の精度を達成しました。」 発表後の質疑応答では、以下のような質問が寄せられていました。 司会からの質問:今回の実装ではXilinx DPUコアによる物体検出処理と、RISC-Vを用いたトラッキング処理を1つのプログラムではなく、2つのプログラムで実装・動作させていました。 ninfueng氏からの回答:はい。DPUコアとRISC-Vを1つに実装することでシステム的に難易度が上がることから、別々に実装することで、実装にかかわるリスク・ハードルを下げることを選択しました。 司会からの質問:なぜ、トラッキングアルゴリズムとしてSORTを選択しましたか? ninfueng氏からの回答:3つ理由があります。1つはオープンソースとして公開されていた。2つ目に一時期トラッキングの分野で、先進アルゴリズムとして知られていた。加えて、シンプルオペレーションによる実装であった点から、SORTを選択しています。 続いて、同じくアイデア賞に入賞されたチームVertical _Beachの皆さんに、解法についてご説明いただきました。

アイデア賞

チームVertical_Beach

「第4回に引き続き、2名で参加させていただきました。今回はこれまでのコンテストと比較して難易度が高かったため、提出することを目標に開発を進めました。物体追跡のアルゴリズムについては、物体検出と物体追跡を分けて実装を進められるTraking-by-detection方式を採用しています。物体検出についてはXilinx DPUを使用することで、実装を容易にしました。RISC-Vに関しては、一から自分で実装するのではなく、公開されている既存の実装を流用することで、実装の難易度を軽くしました。最終成果物は、MOTAが0.2807344だったため、処理速度賞に入るための0.60に達することはできませんでした。システム概要としては、FPGA領域にはXilinx DPUと、VexRiscvというRISC-Vコアを使っています。ソフトウェアの構成は、Xilinx DPUでYOLOv4-tiny、トラッキングアルゴリズムはByteTrackで行いました。基本的にはARMコアで処理を行いましたが、一部をRISC-Vにオフロードする形にしています。ご清聴ありがとうございました。」 発表後には、以下のような質問が寄せられました。 視聴者からの質問:もっと時間があれば、試したかったことはありますか? チームVertical_Beachの回答:ハードウェアについては、RISC-Vの拡張命令の実装を行いたかったです。ソフトウェアについては、他のアルゴリズムもいくつか試してみたかったという心残りがあります。 視聴者からの質問:第4回と比較して、特に難しかったのはどういった点でしたか? チームVertical_Beachの回答:ハードウェアの観点では、第2回、第4回ともに基本的にはDPUの上で動く高速なモデルを作ることが目的だったんですが、今回はRISC-Vを載せないといけなかったため、Vitisフローについて勉強するなど、学習すべきことが多かったのが難しかったです。ソフトウェアも、RISC-Vを使うことでアルゴリズムが複雑化して苦労しました。 最後にプレゼンテーションを行ったのは、同じくアイデア賞に輝いたs.yamashitaさん。解法について、丁寧にご説明いただきました。

アイデア賞

s.yamashita 氏

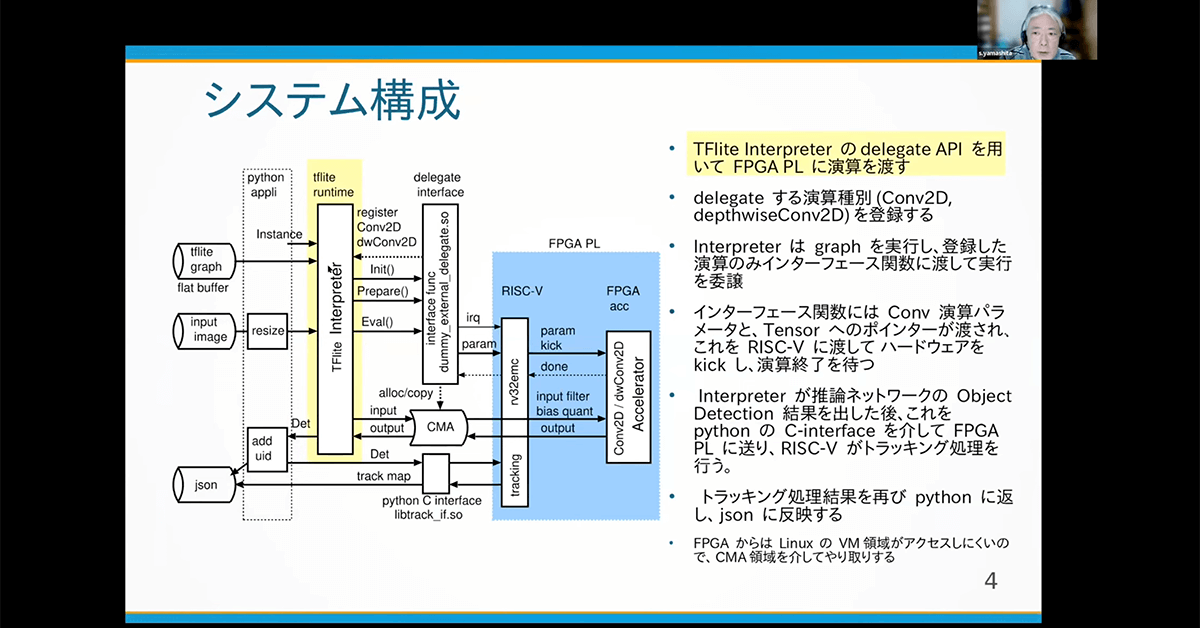

「私はTensorFlow Liteのdelegate機構を用いたアクセラレータと、rv32emcというRISC-Vを用いて実装を行いました。このRISC-Vを実装するにあたって、CPUcoreをscratchから開発しています。また、アクセラレータの実行制御と物体検出結果からのトラッキング処理は、1つのRISC-Vで行いました。実装方法については、アクセラレータ、RISC V coreともにSystemVerilogを用いたRTL記述で行っています。このように、ハードウェア全体をRTL記述で行ったことが一番の特徴だと思います。最終的な成果物はリーダーボード上の評価で0.11、Ultra96-V2上での実行時間は261ms/frameだったので、スコアも速度も上げることができなかったのが残念です。速度を上げることができなかった理由として、MACの並列数が42にとどまってしまったことが大きいと思います。この課題を解決するためには、outputチャンネルを4~8並列にして2次元の並列化を行うことが有効だと考えています。発表は以上になります。ありがとうございました。」 発表後には、以下のような質問が寄せられました。 視聴者からの質問:今回FPGAをフルクスラッチで実装したとのことですが、FPGAのデバッグにあたってどのような手法を用いたのでしょうか? s.yamashita氏の回答:RISC-Vに関しては、最初にターミナルが動くようにすることで、そのターミナルを介してテストプログラムを実行させてデバッグしました。また、シミュレーションでは検知できなかったバグが発生することを想定して、ロジックアナライザを組み込んでデバッグしました。 視聴者からの質問:RISC-Vの実装は難しかったでしょうか? s.yamashita氏の回答:RISC-Vの命令セットは非常にシンプルでよく考えられたものなので、実装は比較的容易に感じました。以前、命令セットでCPUを組んだことがあったのですが、そちらの方が自分にとっては難しかったです。 以上で、全ての解法プレゼンテーションが終了。その後、AIエッジコンテストのステアリングコミッティ審査会のソニーセミコンダクタソリューションズ株式会社 松本氏と、東京工業大学 工学院情報通信系 中原教授の2名による講評が行われました。

ソニーセミコンダクタソリューションズ株式会社 システムソリューション事業部 Distinguished Engineer 松本 浩彰 氏

「入賞された皆様おめでとうございます。総合力を必要とする今回のコンペティションは、今後に役立つ重要な経験になったのではないでしょうか。アイデア賞に選ばれた3チームの方々についてコメントをさせていただくと、ninfuengさんは、性能測定まで漕ぎ着けていただいたのが非常に素晴らしかったと思います。チームVertical_Beachは、トレンドのアルゴリズムを活用した点が特徴的でした。また他の参加者や今後に役立つ記事を書いてくださり大変ありがたかったです。s.yamashitaさんは、このコンペティションで求められている趣旨に沿った開発スタイルで進めてくださったのが素晴らしかったと感じています。前回のコンペティションの資産を活かしたことや、RISC-Vを自ら作成するなどの工夫をされていたのも評価された点だと思います。今回培ったノウハウは次回にも活きてくると思うので、ぜひ次回も参加していただけると幸いです。」

東京工業大学 工学院情報通信系 准教授 中原 啓貴 氏

「今回のコンペティションは作業量が多いため、一人で進めるのは大変だったと思うのですが、想定以上にたくさんの方にご参加いただいたこと、とても嬉しく思います。今回入賞された方以外にも、とてもいいアイデアが数多く見られたのが印象的でした。このコンペティションは、ハードウェア、AI、OSなど多様な技術を扱うため、参加を通じて自分のスキルセットの中で何が秀でているのか、逆にどこを伸ばすべきかがみえてきたのではないでしょうか。ぜひ、次回以降も奮ってご参加いただければと思います。」 最後に、AIエッジコンテストのアドバイザリーコミッティ委員長のカーネギーメロン大学 金出教授より総評をいただき、閉会となりました。

カーネギーメロン大学 金出 武雄 教授

「ご入賞された方々、おめでとうございます。どう工夫するか、どう進めるかなどさまざまな視点から考察されていて、とても興味深く発表を聞かせていただきました。私は半世紀以上こうした分野を専門にしていますが、今日に至るまで、アルゴリズムのレベルで高速にハードウェア化するにはどういった性質が必要なのか、もしくはどういったプロセスがそれを可能にするのか、数多くの研究がされてきました。今後その次のレベルに進むにあたって、今回のコンペティションは新たな技術につながる最初の一歩になったと言えるかもしれません。だからこそ、こうしたコンペティションを継続させていくことが大切だと実感いたしました。本日は本当にありがとうございました。」

まとめ

AIモデル開発のスキルだけでなくハードウェア開発のスキルも求められるため、非常に難易度が高かった今回のコンペティション。それにも関わらず、多くの方がその難しさと正面から向き合い、数々のアイデアを生み出していたことに思わず胸が熱くなりました。限られた時間の中で諦めることなく課題に取り組み、壁を乗り越えた参加者の皆様に、心からの大きな拍手を贈りたいです。こうしたコンペティションによって広く知を募り、技術の革新と未来のAIエッジ技術を担う人材を発掘することが、さらに便利で安心な社会の実現につながることを願っています。 なお、第1回~5回のAIエッジコンテストの概要や実績データについては以下のリンクからご確認いただけます。 ・AI Edge Contest総合サイト ・第1回AIエッジコンテスト(アルゴリズムコンテスト①) ・第2回AIエッジコンテスト(実装コンテスト①) ・第3回AIエッジコンテスト(アルゴリズムコンテスト②) ・第4回AIエッジコンテスト(実装コンテスト②) ・第5回AIエッジコンテスト(実装コンテスト③) ・【関連記事まとめ】第4回AIエッジコンテスト (実装コンテスト②)~FPGAを使った自動車走行画像認識~