March 17, 2021 Winners' reports have been released.

February 2, 2021 The final ranking is reflected on the leaderboard. (The winners of the idea award indicate the final ranking as "4th")

January 29, 2021 The online awards ceremony will be held on February 13th. At the award ceremony, the winners will also give a presentation. If you would like to attend, please apply from here.

December 1, 2020 The provisional processing time has been posted.

November 26, 2020 Acceptance of processing time for provisional ranking has started. Please submit from the following form by October 31.Provisional performance application form

November 6, 2020 "Awards" has been updated.

November 5, 2020 The provisional processing time has been posted.

October 16, 2020 The video and material of the FPGA online seminar held in August has been released.Online seminar video

October 8, 2020 Acceptance of processing time for provisional ranking has started. Please submit from the following form by October 31.Provisional performance application form

July 22, 2020 Application for participation in FPGA online seminar (August 8) will start. At the seminar, we will hold the awards and presentations of the winners of the 2nd contest. If you would like to participate, please apply below.

Application for seminar

July 17, 2020 We are now accepting applications for FPGA boards. If you would like to apply, please apply using the "Board offer document examination application form" button in the center of the screen.

Purpose

With the progress of artificial intelligence (AI) technology, social implementation such as image recognition using AI technology, automatic driving, and natural language processing is rapidly progressing. Especially in the edge computing field, since it is necessary to realize AI technology with higher efficiency, startups mainly in the United States and China and major vendors are accelerating their entry into AI hardware, and even in Japan Not only that, there is an urgent need to develop human resources and industries for hardware to accelerate AI processing such as LSI and FPGA.

Against this background, we will carry out this contest, in addition to the conventional AI technology development centered on software, we are aiming to develop human resources and startups with AI hardware in mind, as well as industry development utilizing these technologies. In this contest, we will develop AI hardware using FPGA and set the hardware system development that considers edge computing including hardware and software (network model and system optimization) as an issue.

The 1st AI Edge Contest (Algorithm Contest (1))

The 2nd AI Edge Contest (Implementation Contest (1))

The 3rd AI Edge Contest (Algorithm Contest (2))

*Please refer to the winners' solutions (source code and report) in the 2nd AI edge contest (implementation contest (1)) using FPGA.

Contest Outline

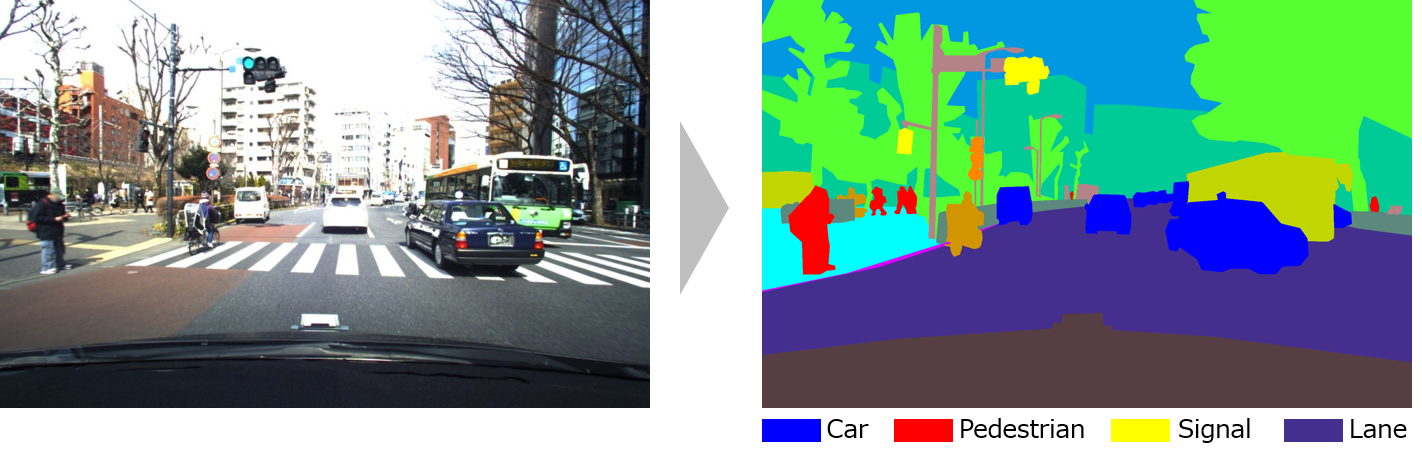

| Subject | (Algorithm development) Create an algorithm to segment at the pixel level the region corresponding to an object from a vehicle front camera image. (Algorithm implementation) Design hardware accelerators and implement algorithm on the target FPGA board. |

| Provided data | (Train/Test) Image of the vehicle front camera (Train) Split-labeled region corresponding to an object at the pixel level (Train) Image meta information (route/time of day, etc.) |

| Identifying target | Car, Pedestrian, Signal, Lane |

| Platform | Avnet Ultra96 FPGA board |

| Evaluation | - The evaluation is the processing speed of the target FPGA board. - However, in order to be the target of evaluation, the goodness of the segmentation result (=prediction result for the test data) must meet the standard or more. - IoU is used as a measure of the goodness of the segmentation result, and IoU = 0.6 or more is the requirement standard. (The idea award is not limited to this) - The IoU requirement standard values are subject to change. |

| Awards |

Processing speed Award 1st Prize: The 1st Prize Trophy / 400,000 yen + Google Cloud Platform Coupon (100,000 yen) 2nd Prize: The 2nd Prize Trophy / 200,000 yen + Google Cloud Platform Coupon (50,000 yen) 3rd Prize: The 3rd Prize Trophy / 100,000 yen + Google Cloud Platform Coupon (50,000 yen) Idea Award Idea Award Trophy / 100,000 yen(Up to 3 team) |

Subject (Algorithm Development)

Color coding is applied on a pixel-by-pixel basis for areas containing objects to be detected in images taken vehicle front camera. The following four categories are used for objects to be utilized in prediction:

・Car

・Pedestrian

・Signal

・Lane

* Python source code to convert from PNG-format color-coded image files to JSON-format application files can be downloaded from the data page.

Subject (Algorithm Implementation)

Implement developed algorithm into Avnet Ultra96 (Zynq UltraScale+ MPSoC ZAU3EG SBVA484) FPGA board.

Data

| Train | Test | |

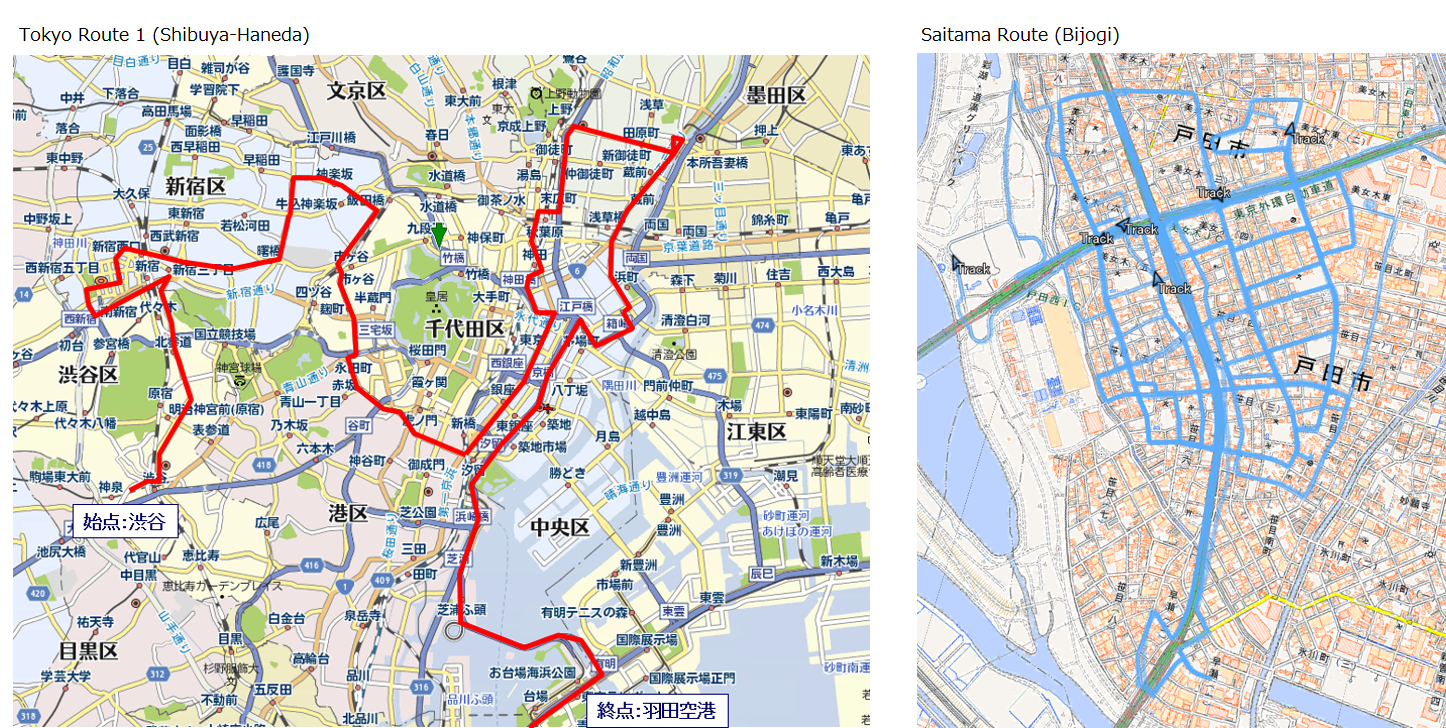

| Route | Tokyo Route 1 (Shibuya-Haneda)),Tokyo Route 2 (Kagurazaka), Saitama Route (Bijogi) | |

| Time of day | 3 time categories of "morning," "day" and "night"; only "day" is used for Tokyo Route 2, and only "morning" is used for the Saitama Route | |

| Resolution | 1936 x 1216 | |

| Photography interval | 10 seconds for Tokyo Routes 1 and 2, and 30 seconds for the Saitama Route (varies in some cases) | |

| Category | Car, Pedestrian, Signal, Lane, Bus, Truck, SVehicle, Motorbike, Bicycle, Signs, Sky, Building, Natural, Wall, Ground, Sidewalk, RoadShoulder, Obstacle, others, own | Car, Pedestrian, Signal, Lane |

| No. of Images | 2,243 | 649 |

Route

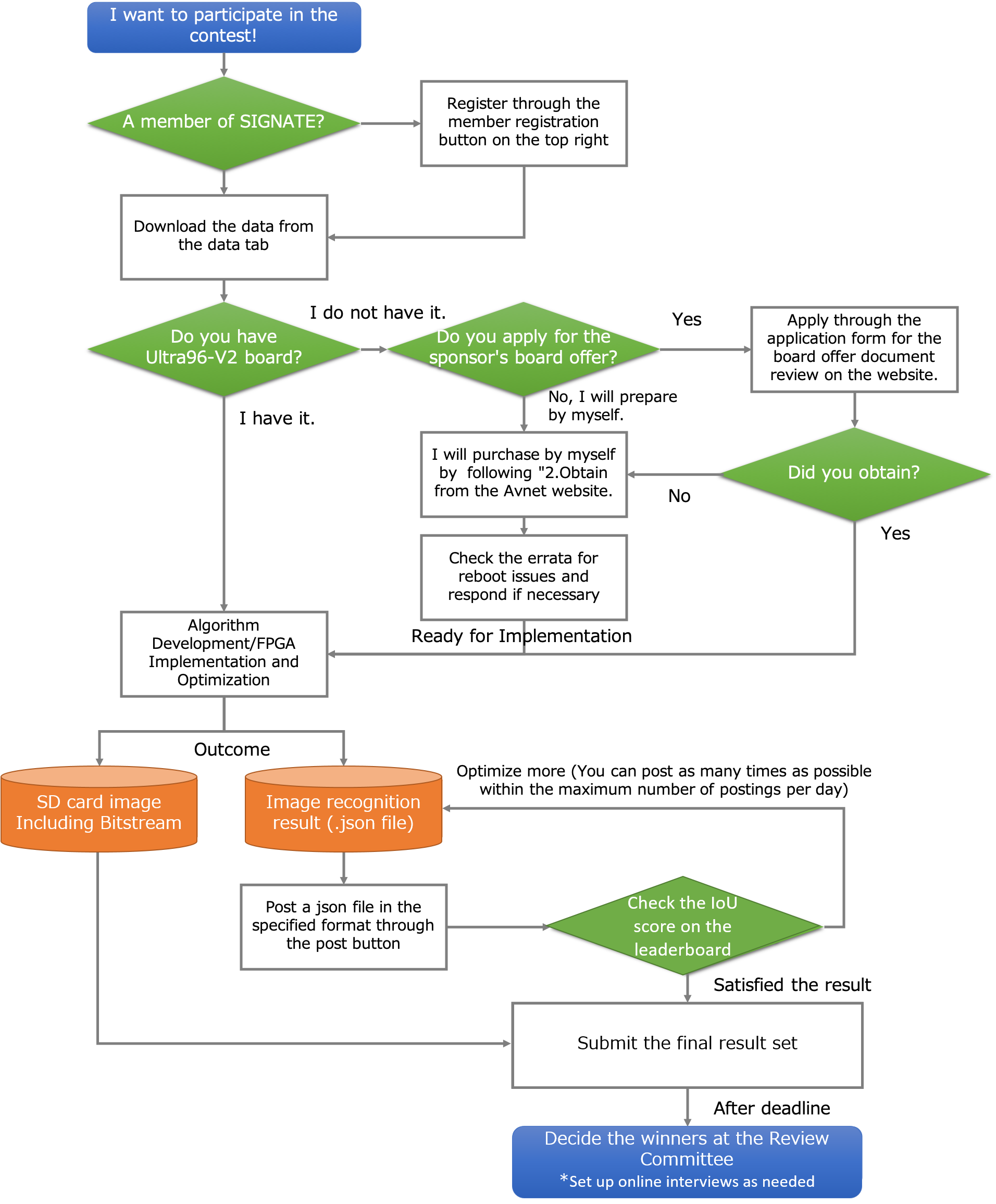

Flow of entry / registration for the contest

1. Sign up for SIGNATE (Please register through the member registration button on the top right of the page if you are not currently a member.).

2. Download the data from the data tab (Please agree the terms of entry that will be displayed when downloading.).

3. Prepare the Ultra96-V2 board (if you do not have one, you can purchase it by yourself or apply through the application form.).

*We plan to provide FPGA board to a maximum of 80 applicants based on the review of application among the people who apply through application form for the board offer document review. Please apply from the button below if you would like to get the FPGA board offer to use for this contest.

4. Algorithm development, FPGA implementation and optimization.

5. During the contest, submit the segmentation result from the "Submit" button on the upper right of this page and check the IoU score on the leaderboard.

*The IoU score until the last day of the contest (public score) and the IoU score after the contest (private score) are the same.

*Please refer to the IoU function that can be downloaded on the data page

6. Submit the final result set by the end of the contest.

*For details, refer to "submission_details.pdf" that can be downloaded from the data page.

*Upload on the Internet such as Dropbox, Gigafile, etc., and inform us of the information required for downloading to the following form.

Participation information is being registered. Please wait for a while.

Participation information is being registered. Please wait for a while.