Oct 16, 2020 Winner's presentation videos have been released.

Winners presentation video

July 22, 2020 We will start application for online award ceremony and winner presentation (8/8). The award ceremony will also include an FPGA online seminar for the 4th contest that is currently being held. If you would like to participate, please apply below.

Application for the award ceremony

June 1, 2020 In the solusion tab, we have posted the source code link and report of the prize winner, and the result of the performance evaluation of the applicant.

March 5, 2020 The set of final result application form has been set up at the bottom of the data page. March 2, 2020 Clarified the definition of the section to measure the inference time. (Evaluation) February 25, 2020 Updated the sample of a trained network based on Tiny Yolo v3.

February 25, 2020 Updated materials for submission details.

February 19, 2020 The materials used in the FPGA seminar have been uploaded to the data page.

February 6, 2020 The outline of 2020/2/6 FPGA seminar has been released. If you would like to participate, please apply from the "FPGA Seminar Participation Application Form" at the bottom of the page.

February 6, 2020 The team creation deadline has been extended to February 29, 2020.

January 23, 2020 "Awards" has been updated.

January 8, 2020 Evaluation criteria have been finalized. In addition, a sample of a trained network based on Tiny Yolo v3, which is the basis for setting, has been uploaded to the data page.

December 11, 2019 An article about the contest has been published on EDA EXPRESS.

December 5, 2019 The data which organized the details of the submission was uploaded to the data page.

November 21, 2019 The flow of entry / registration for the contest and the decision method for winners were added.

November 19, 2019 Registration of FPGA board offers started.

Purpose

As startup companies and major vendors have been aggressively entering AI hardware market mainly in the United States and China, it is an urgent issue in Japan to develop human resources and industry of the hardware market in order to accelerate AI processing including LSI and FPGA as well as software.

In light of such situation, we will hold this contest for the purpose of development of C-based composed HLS introduced as a development of AI hardware - RTL design - LSI development as well as development of startup and industry.

Contest Outline

| Subject | (Algorithm development) Create an algorithm to detect a rectangular area including objects from the image of vehicle front camera. (Algorithm implementation) Design hardware accelerators and implement algorithm on the target FPGA board. |

| Provided data | (Train/Test) Image of the vehicle front camera (Train) Rectangular area labeled with objects (Train) Image meta information (travel route/time of day, etc.) |

| Identifying target | Car, Pedestrian, Truck, Bicycle, Signal, Sign |

| Platform | Avnet Ultra96 FPGA board |

| Submissions | ・Software/HLS or a set of RTL ・Composed log (size, composed estimated data of electric power) ・Measurement results by performance ・Report (Option, It is not mandatory. Free style.) *Template and submission method will be announced later. |

| Awards | <Best Performance Award> 1st Prize: The Ministry of Economy, Trade and Industry Commerce Information Policy Bureau director award / The Extreme Edge Award / The 1st Prize Trophy / 500,000 yen + Google Cloud Platform Coupon (100,000 yen) 2nd Prize: The Extreme Edge Award / The 2nd Prize Trophy / 300,000 yen + Google Cloud Platform Coupon (50,000 yen) 3rd Prize: The Extreme Edge Award / The 3rd Prize Trophy / 100,000 yen + Google Cloud Platform Coupon (50,000 yen) <Idea Award> |

| Collaboration with other competitions | Higher ranking winners of the contest can be qualified to participate in the “Autonomous Driving AI Challenge"which is scheduled to be held by the Japan Automobile Engineering Society in June 2020, and can challenge to implement algorithm into the automatic driving program, to equip it into a cart vehicle and to drive its vehicle. |

Subject (Algorithm Development)

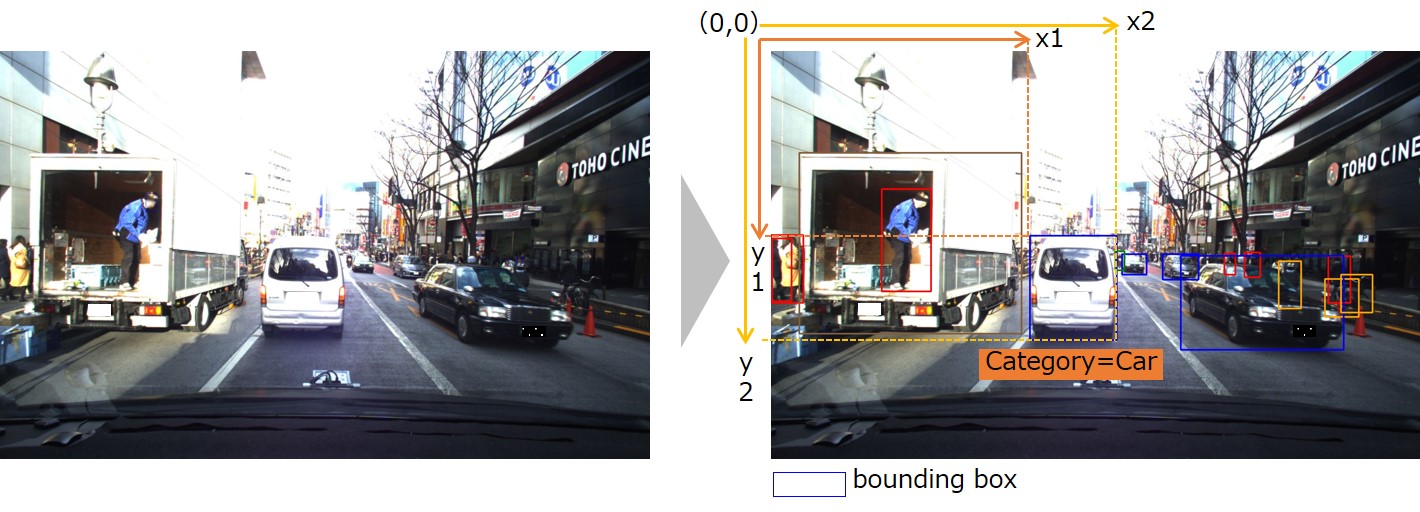

Assign a rectangular area including predictive object as bounding box=(x1,y1,x2, y2) toward the image of the vehicle front camera and give one category. More than one bounding boxes are assigned on each image and a bounding box is indicated by specifying 4 points of the top left coordinates (x1, y1) and bottom right coordinates (x2, y2) in the object area as the origin (0,0) on the top left coordinates on the image.

Predictive target objects are following 6 categories.

・Car

・Truck

・Pedestrian

・Bicycle

・Signal

・Signs

Subject (Algorithm Implementation)

Implement developed algorithm into Avnet Ultra96 (Zynq UltraScale+ MPSoC ZAU3EG SBVA484) FPGA board. We plan to provide FPGA board to a maximum of 80 applicants based on the review of application among the people who apply through application form for the board offer document review. Please apply from the button below if you would like to get the FPGA board offer to use for this contest.

Data

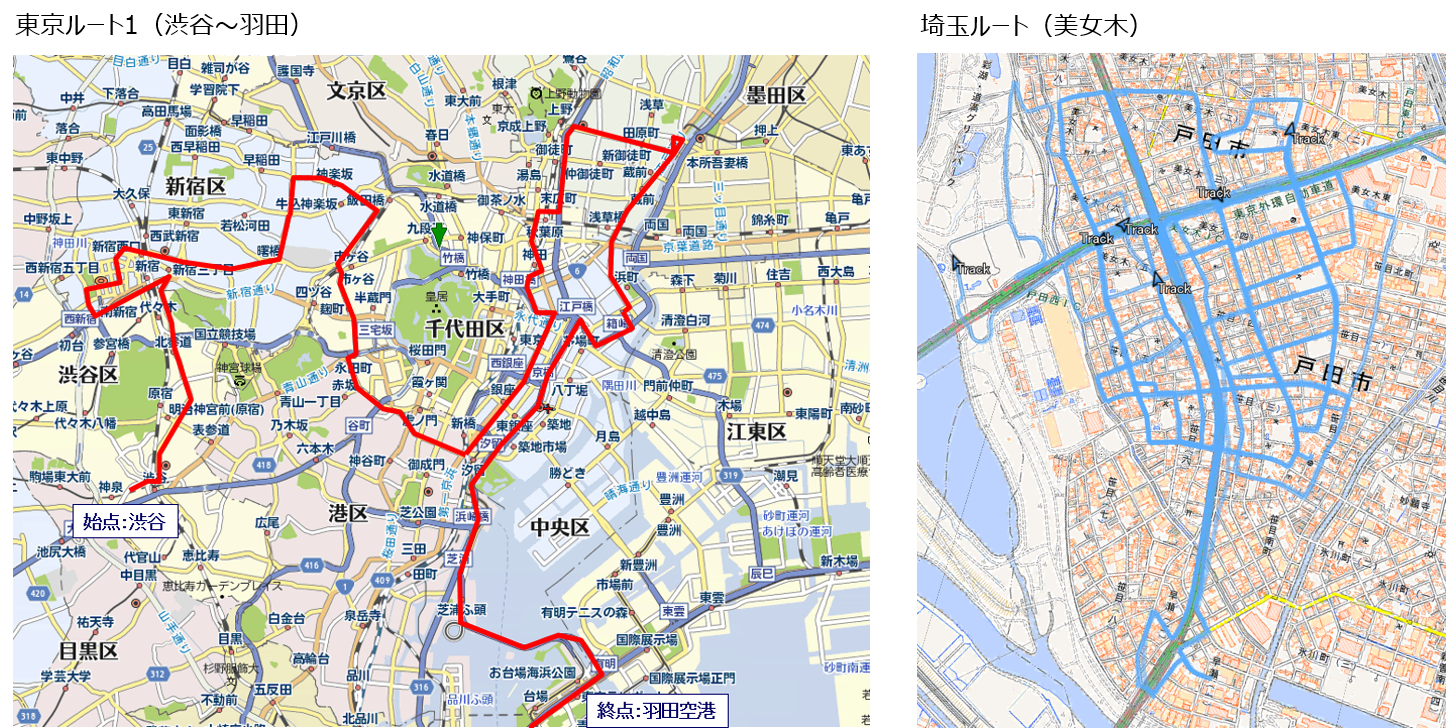

Route:Tokyo Route1 (Shibuya - Haneda), Tokyo Route2 (Kagurazaka), Saitama Route (Bijogi)

Time of day:Morning/Daytime/Night (Only Daytime for Tokyo Route2 (Kagurazaka))

Shooting interval:One second (*There are some exceptions.)

Resolution:1936 x 1216

Number of Images:(For Train) 21,258 images, (For Test) 6,355 images

Number of Categories:10

Category Types:Passenger Car (Car), Pedestrian (Pedestrian), Truck (Truck), Signal (Signal), Signs (Signs), Bicycle (Bicycle), Motorbike (Motorbike), Bus (Bus), Special Vehicle (Svehicle), Train (Train)

Travel Route

Tokyo Route 1 (Shibuya - Haneda) Saitama Route (Bijogi)

Flow of entry / registration for the contest

1. Sign up for SIGNATE (Please register through the member registration button on the top right of the page if you are not currently a member.).

2. Download the data from the data tab (Please agree the terms of entry that will be displayed when downloading.).

3. Prepare the Ultra96-V2 board (if you do not have one, you can purchase it by yourself or apply through the application form for the board offer document review on the website.).

4. Algorithm development, FPGA implementation and optimization.

5. Check the Precision by posting predictive result through the post button.

6. Submit the set of final result by the end of the contest.(application form has been set up at the bottom of the data page.)

Reference information for obtaining the Ultra96 board to use for this contest

・Subjected board for this contest is Ultra96-V2.

・Regarding method to obtain: There are two ways to obtain it.

1. Provided from this contest

- Although limited in number, the Ultra96 board will be provided after review for the contest participants. For those of you who wish to be provided, please apply through the "application form for board offer document review".

- Provided board includes an AC adapter, power conversion cable, and JTAG board.

2. Obtain from the Avnet website

- You can purchase from here.

- We recommend you to purchase the following related parts along the purchasing of the board.

・JTAG board for Ultra96: It is necessary to connect the UART (serial) consol.

・Avnet recommended AC adapter, power conversion cable

- Power supply

- Conversion connector

Regarding the errata of Ultra96 board

The errata from Avnet is published the following site.

http://avnet.me/Ultra96-V2_Errata

The errata particularly has the following known issues:

・Reboot issue of Ultra96-V2

- Ultra96-V2 When the load of the PL part goes up high, MPSoC reboots.

- Ultra96-V2 It is posted on the errata reporting page.

This is caused by the reset operation in MPSoC that was triggered by the PowerGood signal's drop when a specific threshold is exceeded while the IC called PMIC is monitoring the Vccint voltage.

- There is no margin for this threshold setting in the current V2 board, and a reset is applied when a set threshold is exceeded due to increase in current consumption of the PL section.

- The limit is 3A for the current ULtra96v2.

・The limit of this errata can be relieved to about 5A by revising the board and changing the setting of PMIC. A complete set of countermeasure procedures prepared by Avnet can be downloaded from below.

20191114_Ultra96-V2 PMIC update procedure.zip (This can be obtained by the data tab on this website)

Infinion that is required for the measures of this issue.

The sales information of USB005 writing cable is as follows.

Mouser

Digikey

Chip1Stop

・We plan to provide this revised board for the board offered from this contest.

FPGA seminar for AI edge contest

In conducting the FPGA implementation contest of the AI edge contest, we held a seminar on edge deep learning processing using FPGA for software and AI engineers who are interested in hardware implementation such as FPGA, and applied for the contest. Aim to accelerate human resource development through contest application, along with providing opportunities.

Overview

Date: 13:30-17:00, Tuesday, February 18 (Reception starts at 13:00-)

Location: Innotec Building 2F Seminar Room

agenda:

13:00: Venue open

13: 30-13: 50 (20min) Opening remarks and introduction of the contest (Saito of NEDO, Obuchi of Digital Media Professional)

13: 50-14: 35 (45min) FPGA Seminar # 1 (Koyama of FPGA Information)

14: 35-14: 50 (15min) break

14: 50-15: 35 (45min) ML learning platform of Google Cloud to be used in AI edge development (Sato of Google)

15: 35-16: 50 (75min) FPGA seminar # 2 (Koyama of FPGA Information)

16: 50-17: 00 (10min) Wrap-up, Q&A throughout (Obuchi of Digital Media Professional)

Information for the day

Reception desk: Innotek Building 1F (3-17-6 Shin-Yokohama, Kohoku-ku, Yokohama 222-8580)

Reception start time: 13:00, Tuesday, February 18

Reception method:

Please receive the "Building Admission Sticker" at the dedicated reception on the right side of the 1F front entrance, and go up to the 2nd floor using the entrance stairs.

Please give your reception number in the front room of the 2F seminar room. Please hand one business card at that time. (If you do not have a business card, please let us know.)

Participation information is being registered. Please wait for a while.

Participation information is being registered. Please wait for a while.